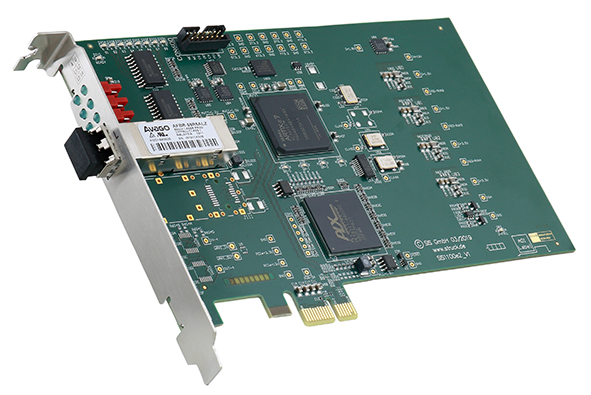

SIS1100-e2 PCI Express optical link board

The SIS1100-e2 is the follow up card to our SIS1100-eCMC board (without CMC carrier functionality). It was developed to extend the lify cycle of our PCIe to VME interface. For software/driver compatibility reasons we still employ the PEX8311 PCI Express to local bus bridge chip.

The PCI Express Gen2 interface of the Artix-7 FPGA can be used directly (and the PEX8311 omitted) for custom applications.

|

|  |

Features/Properties: |

SIS1100-e2 PEX8311 EEPROM File

Prefetchable base address capability has to be enabled on the PEX8311 PCI Express to local bus bridge chip to perform 64-bit direct master or DMA transfers. This is of relevance on machines from 4 GB of memory on. The corresponding bits can be set through the configuration EEPROM of the PEX8311. Units with serial number 94 and higher are shipped with this configuration. The EEPROM can be regrogrammed with the PLX Technology SDK. The V2 EEPROM file can be found here.An archive with upgrade instructions and software is available here.